# ST7282A5 - ST7282B5

# ROM FROM EPROM

#### PRELIMINARY DATASHEET

- ST72-Core

- Controller/Driver for max. 20 × 16, 28 × 8 or 32 × 4

- LCD segments (ST7LCD4)

- 56 bytes LCD-RAM

- 864 bytes data RAM

- 512 bytes EEPROM (eep2a)

- 32Kbytes program ROM

- 24 digital I/O (ST7 IO3) with pull up, interrupt input, analog input, push-pull/ open drain output

- 36 LCD/IO combi pins (ST7 LCIO1) with pull-up, interrupt input, push-pull, open drain output, LCD output

- 16 bit reload timer (ST7TIM4)

- Watchdog Timer (ST7 WD2)

n

- 8 bit synchronous serial I/O (ST7SIO)

- 8 bit A/D Converter (ST7ADC2)

- RDS Demodulator (ST7 RDS BD)

- Group & Block Sync Module for RDS (ST7 RDS GB)

- RDS filter (ST7 RDS FI)

- LCD Synchro IN / Out

- System Frequency 8.55 MHz

| Family | Issuer Ref. | Chrono   | March 26, 1997                       | Previous Ref | Edition  |

|--------|-------------|----------|--------------------------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON                          |              | Target C |

| 517    | PG-RO       | 7282A5B5 | ATZ, SGS-IHOMSON<br>MICROELECTRONICS | Page         | 1/23     |

# **1 GENERAL DESCRIPTION**

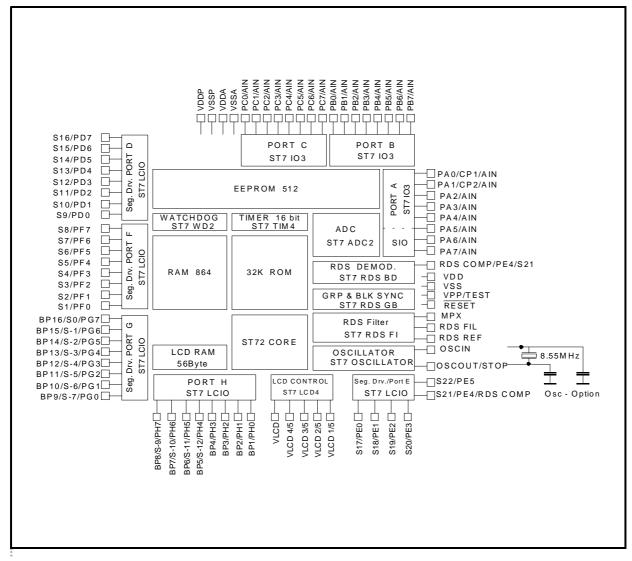

#### Figure 1. Block Diagram

| Family | Issuer Ref. | Chrono   | March 26, 1997       | Previous Ref | Edition  |

|--------|-------------|----------|----------------------|--------------|----------|

| ST2    | PG-RO       | 97115    | SGS-THOMSON          |              | Target C |

| ST7    | PG-RO       | 7282A5B5 | AT. MICROELECTRONICS | Page         | 2/23     |

#### 1.1 Quick Reference

The ST7282A5/B5 is a 32K ROM version of the ST72 family, using the ST72CORE and N-Well technology.

It is derived from EPROM M4 version replacing EPROM by ROM.

Two different commercial products are supported by this device : ST7282A5 (no LCD driver) functionnality described in specification SD70KL1618 ed. F) and ST7282B5 (LCD driver) functionnality described in specification 96096 ed. B).

It contains an LCD controller/driver with 20 segment and 16 backplane outputs able to drive up to  $20 \times 16 = 320$  segments.

The LCD control logic reads automatically data from the LCD-RAM independently from the ST7282 B5.

Further it contains up to 62 I/O pins, 24 of them can be used as analog inputs to the 8 bit analogdigital converter. Each digital I/O pin can individually be defined by software to work in one of the following modes: open-drain output, push pull output, input, input with pull-up (23 pins only) or interrupt input with pull up (23 pins only). 3 of the digital I/O pins serve as interface to the SIO. On pin PA4 the pull-up resistor is desactivated.

Port pins PD, PE, PF, PG and PH are multiplexed with LCD Segment and backplane pins.

A 512 byte EEPROM for non volatile storage of data is available. The programming voltage for that device is generated on chip without external components. So no extra supply is necessary. 16 bytes are protected against external readout.

One interrupt vector is connected to the I/O ports. Five more interrupt vectors are available for the timer, the ADC, the serial I/O interface and the Group & Block Sync module (2). The watchdog can be set by the user in 64 increments from 2.8msec to 182msec ( $f_{OSC} = 8.55$  MHz).

A synchronous 8 bit serial interface for serial data IN/OUT is also implemented.

RDS signals can be decoded with the help of RDS filter, RDS demodulator and Group & Block Sync module.

#### **1.2 Parameters**

The values below substitute the corresponding values in the specifications of dedicated functions.

#### 1.2.1 Absolute maximum ratings

| Supply voltage         | ( V <sub>DD</sub> - V <sub>SS</sub> ) | -0.3 +7V                                     |

|------------------------|---------------------------------------|----------------------------------------------|

| Input voltage*         | V <sub>IN</sub>                       | V <sub>SS</sub> -0.3VV <sub>DD</sub> +0.3V   |

| Output voltage*        | <b>V</b> OUT                          | V <sub>SS</sub> -0.3V V <sub>DD</sub> +0.3V  |

| Input current          | l <sub>in</sub>                       | -10 +10mA                                    |

| Output current*        | IOUT                                  | -10 + 10mA                                   |

| Power dissipation      | P <sub>D</sub>                        | tbd                                          |

| Storage temperature    | T <sub>stg</sub>                      | -55 +125°C                                   |

| Operation temperature  | Tamb                                  | -40 +85°C                                    |

| Display voltage        | (V <sub>LCD</sub> - V <sub>SS</sub> ) | V <sub>DD</sub> 7V                           |

| Output voltage Seg+COM | V <sub>OUT</sub>                      | V <sub>SS</sub> -0.3V V <sub>LCD</sub> +0.3V |

| ESD                    | ESD                                   | 2500V                                        |

| LU susceptibility      | LU                                    | V <sub>DDA</sub> , Pin 52 - Class C          |

#### 1.2.2 Recommended operating conditions

| Supply voltage           | (V <sub>DD</sub> - V <sub>SS</sub> )                                                                                 | 4.5 5.5V |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|----------|

| Supply votage difference | (V <sub>DD</sub> , V <sub>DDP</sub> , V <sub>DDA</sub> )<br>(V <sub>SS</sub> , V <sub>SSP</sub> , V <sub>SSA</sub> ) | 50mV     |

The maximum accumulated current of all I/O pins should not exceed 40 mA for  $V_{\mbox{DDP}}$  and 40 mA for  $V_{\mbox{SSP}}.$

\* except LCD pins

\*\* MIL 883B Mode, 100pF through 1.5k

| Family | Issuer Ref. | Chrono   | March 26, 1997                      | Previous Ref | Edition  |

|--------|-------------|----------|-------------------------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON                         |              | Target C |

| 517 F  |             | 7282A5B5 | AT. SGS-INUMSUN<br>MICROELECTRONICS | Page         | 9/23     |

#### **1.2.3 Electrical Characteristics**

The values given in the specifications of dedicated functions are generally not applicable for chips. Therefore, only the limits listed below are valid for the product. T = -40 ... +85°C,  $V_{DD}$  -  $V_{SS}$  = 5V unless otherwise specified.

| PAR                                                                                        | AMETER                                                |                  | SYMBOL                                                                                  | CONDITION                                                                                                        | MIN                                 | TYP                             | MAX                                         | UNIT                               |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------|---------------------------------------------|------------------------------------|

| Supply voltage                                                                             | ge                                                    |                  | V <sub>DD</sub>                                                                         |                                                                                                                  | 4.5                                 | -                               | 5.5                                         | V                                  |

| Supply curre                                                                               | ent Run Mode                                          |                  | I <sub>DD</sub>                                                                         | f <sub>OSC</sub> =8.55MHz<br>no output load                                                                      | -                                   | 10                              | 20                                          | mA                                 |

| Supply curre                                                                               | ent Wait Mode                                         | e                | I <sub>DD</sub>                                                                         | f <sub>OSC</sub> =8.55MHz<br>WD, Timer, LCD active                                                               | -                                   | 3                               | 5                                           | mA                                 |

| Supply curre                                                                               | ent slow wait r                                       | node             | I <sub>DD</sub>                                                                         | no output load                                                                                                   | -                                   | 0.7                             | 2                                           | mA                                 |

| Supply curre                                                                               | ent halt mode                                         | 1                | I <sub>DD</sub>                                                                         | no output load                                                                                                   | -                                   | -                               | 100                                         | μA                                 |

| Supply curre                                                                               | ent Reset Mo                                          | de               | I <sub>DD</sub>                                                                         | V <sub>RESET</sub> =V <sub>SS</sub><br>f=8.55MHz                                                                 | -                                   | 10                              | 15                                          | mA                                 |

| Display volta                                                                              | age                                                   |                  | V <sub>LCD</sub>                                                                        |                                                                                                                  | V <sub>DD</sub>                     | -                               | 7                                           | V                                  |

| Supply volta<br>(V <sub>DD</sub> , V <sub>DDP</sub><br>(V <sub>SS</sub> , V <sub>SSP</sub> |                                                       |                  | V <sub>D</sub>                                                                          |                                                                                                                  | -                                   | -                               | 50                                          | mV                                 |

| OSCILLATO<br>Input/output<br>Oscillation fr<br>Built up time                               | cap Cin, Cou<br>equency <sup>1)</sup>                 |                  | fosc<br>t <sub>BU</sub>                                                                 | $V_{DD} = 4.5V$<br>$V_{DD} = 5.0V$<br>$C_1 = C_2 = 22pF$                                                         | 8.55<br>-                           | 8.55<br>8                       | 9.00<br>8.55<br>20                          | pF<br>MHz<br>ms                    |

| RESET:<br>Input current<br>Input current<br>Input current<br>Input voltage                 | t <sup>4)</sup><br>t <sup>5)</sup><br>e high<br>e low |                  | -I <sub>R</sub><br>I <sub>R</sub><br>I <sub>R</sub><br>V <sub>R</sub><br>V <sub>R</sub> | Crystal<br>V <sub>R</sub> =V <sub>SS</sub><br>V <sub>R</sub> =V <sub>DD</sub><br>V <sub>R</sub> =V <sub>DD</sub> | -<br>-<br>-<br>0.7V <sub>DD</sub>   | +50<br>+10<br>-<br>-<br>-       | +100<br>+20<br>1<br>-<br>0.2V <sub>DD</sub> | μΑ<br>μΑ<br>mA<br>V<br>V           |

| POWER-ON<br>Supply rise t<br>Supply recov<br>Trigger level<br>Trigger level                | time<br>very time <sup>6)</sup><br>I on<br>I off      |                  | t <sub>r</sub><br>t <sub>rec</sub><br>V <sub>tlon</sub><br>V <sub>tloff</sub>           | 10%-90%                                                                                                          | .01<br>10<br>1.4<br>-               |                                 | 10<br>-<br>-<br>3                           | ms<br>ms<br>V<br>V                 |

| RDS FILTER<br>Center frequ<br>3dB Bandwit<br>Gain<br>Attenuation                           | iency                                                 |                  | fc<br>BW<br>G<br>A                                                                      | $V_{in} = 3mV_{RMS}$<br>57 KHz, $V_{in} = 3mV_{RMS}$<br>$\Delta f = \pm 4$ KHz<br>f = 38 KHz<br>f = 67 KHz       | 56.5<br>2.5<br>18<br>18<br>50<br>35 | 57<br>3<br>20<br>22<br>80<br>50 | 57.5<br>3.5<br>22<br>-<br>-                 | KHz<br>KHz<br>dB<br>dB<br>dB<br>dB |

| Input impeda<br>Load impeda<br>MPX input si                                                | ance                                                  |                  | R <sub>I</sub><br>R <sub>L</sub><br>V <sub>IN</sub>                                     |                                                                                                                  | 100<br>1<br>170                     | 160<br>-<br>250                 | 200<br>-<br>600                             | KΩ<br>MΩ<br>mV <sub>RMS</sub>      |

| Family I                                                                                   | lssuer Ref.                                           | Chron            | D                                                                                       | March 26, 1997                                                                                                   | Previ                               | ious Ref                        | Editio                                      | n                                  |

| ST7                                                                                        | PG-RO                                                 | 97115<br>7282A5I |                                                                                         | SGS-THOMSON<br>MICROELECTRONICS                                                                                  |                                     | Pag                             | Target<br>e 4/23                            | С                                  |

## ST7282A5 - ST7282B5 - ROM FROM EPROM

| PARAMETER                           | SYMBOL              | CONDITION                                   | MIN                | TYP  | MAX                | UNIT  |

|-------------------------------------|---------------------|---------------------------------------------|--------------------|------|--------------------|-------|

|                                     |                     |                                             |                    |      |                    |       |

| I/O PORTS:                          |                     |                                             |                    |      |                    |       |

| Input leakage current 7)            | IIL III             | V=V <sub>SS</sub>                           | -                  | -    | 10                 | μΑ    |

| Input leakage current               | Чн                  | V=V <sub>DD</sub>                           | -                  | -    | 10                 | μΑ    |

| Input voltage high                  | VIH                 | leading edge                                | 0.7V <sub>DD</sub> | -    | -                  | V     |

| Input voltage low                   | VIL                 | trailing edge                               | -                  | -    | 0.2V <sub>DD</sub> | V     |

| Output voltage high                 | V <sub>OH</sub>     | I=5mA, V <sub>DD</sub> =4.5V                | 3.0                | -    | -                  | V     |

| (PA,PB,PC)                          | V <sub>OH</sub>     | I=1.0mA, V <sub>DD</sub> =4.5V              | 4.1                | -    | -                  | V     |

| Output voltage high                 | V <sub>OH</sub>     | I=2.5mA, V <sub>DD</sub> =4.5V              | 3.0                | -    | -                  | V     |

| (PD, PE, PF, PG, PH)                | V <sub>OH</sub>     | I=0.5mA, V <sub>DD</sub> =4.5V              | 4.1                | -    | -                  | V     |

| Output voltage low                  | V <sub>OL</sub>     | I=-5mA, V <sub>DD</sub> =4.5V               | -                  | -    | 1.0                | V     |

| (PA, PB, PC, PD, PE, PF, PG,<br>PH) | V <sub>OL</sub>     | I=-1.6mA, V <sub>DD</sub> =4.5V             | -                  | -    | 0.4                | V     |

| Output voltage slope                | dV <sub>O</sub> /dt | C <sub>I</sub> =50pF                        | -                  | 0.25 | -                  | V/ns  |

| Output current slope                | dl <sub>O</sub> /dt | $C_1 = 50 pF$                               | -                  | 2.5  | -                  | mA/ns |

| Noise amplitude                     | V <sub>N</sub>      | 20MHz-250MHz                                | -                  | 100  | -                  | μV    |

| ·                                   | - 11                | V <sub>IN</sub> =V <sub>SS</sub>            | -                  | -    | -                  | -     |

| Pullup Resistor Current             | I <sub>RPU</sub>    | · IN · 55                                   | -                  | 50   | -                  | μA    |

|                                     |                     |                                             |                    |      |                    |       |

| ADC:                                |                     |                                             |                    |      |                    |       |

| Resolution                          | V <sub>A1</sub>     | f <sub>OSC</sub> =8.55MHz <sup>8)</sup>     |                    | -    | -                  | bit   |

| Total Error                         |                     | f <sub>OSC</sub> =8.55MHz <sup>8)</sup>     |                    | -    | <u>+</u> 2         | LSB   |

| Conversion time                     | t <sub>con</sub>    | f <sub>OSC</sub> =8.55MHz                   |                    | 34   | 35                 | μs    |

| Input capacitance                   |                     |                                             |                    | -    | 5                  | pF    |

| Analog source impedance             | R <sub>VA</sub>     |                                             |                    | -    | 30                 | KΩ    |

| Osc. frequency range                |                     |                                             |                    | 8.55 | -                  | MHz   |

| LCD DRIVER:                         |                     |                                             |                    |      |                    |       |

| Frame frequency                     | f <sub>F</sub>      | f <sub>OSC</sub> =8.55MHz                   |                    | -    | 132                | Hz    |

| DC offset voltage <sup>9)</sup>     | V <sub>OS</sub>     | V <sub>LCD</sub> =V <sub>DD</sub> , no load |                    | -    | 50                 | mV    |

| COM output voltage high             | V <sub>OH</sub>     | I=50μA                                      |                    | -    | -                  | V     |

| COM output voltage low              | V <sub>OL</sub>     | I=50μA                                      |                    | -    | 0.5                | V     |

| SEG output voltage high             | V <sub>OH</sub>     | I=25μA                                      |                    | -    | -                  | V     |

| SEG output voltage low              | V <sub>OL</sub>     | I=25μA                                      |                    | -    | 0.5                | V     |

| EEPROM:                             |                     |                                             |                    |      |                    |       |

| Write time                          | t <sub>W</sub>      | V <sub>DD</sub> =4.5V                       |                    | -    | 10                 | ms    |

1)Operation below 30 KHz Mis possible but requires increased supply current

2)Time to build up the oscillation amplitude to 90%  $V_{\mbox{\tiny DD}}$

3)Pull-up resistor

4)WD not active

5)WD generating a reset

6)Period for which  $V_{\mbox{\tiny DD}}$  has to be disconnected or at OV to allow internal reset function at next power up

7)pull up off

| Family | Issuer Ref. | Chrono   | March 26, 1997   | Previous Ref | Edition  |

|--------|-------------|----------|------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON      |              | Target C |

| 517    | PG-RU       | 7282A5B5 | MICROELECTRONICS | Page         | 5/23     |

8) noise at  $V_{\text{DD}}$ ,  $V_{\text{SS}}$  < 10 mV

9)The DC offset voltage refers to all segment and common outputs. It is the difference between the measured voltage value and nominal voltage value for every voltage level. Rin of voltage meter must be > 10 M $\Omega$ .

| Family | Issuer Ref. | Chrono   | March 26, 1997 | Previous Ref | Edition  |

|--------|-------------|----------|----------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON    |              | Target C |

| 517    | PG-RO       | 7282A5B5 |                | Page         | 6/23     |

#### 1.3 ST7282A5/B5 ADDRESS MAPPING

| ADDR.      | USER                       |

|------------|----------------------------|

| \$0000     | Port A Data Reg.           |

| \$0001     | Port A Data Direction Reg. |

| \$0002     | Port A Option Reg.         |

| \$0003     | Port A Pin status          |

|            |                            |

| \$0004     | Port B Data Reg.           |

| \$0005     | Port B Data Direction Reg. |

| \$0006     | Port B Option Reg.         |

| \$0007     | Port B Pin status          |

| \$0008     | Port C Data Reg.           |

| \$0009     | Port C Data Direction Reg. |

| \$000A     | Port C Option Reg.         |

| \$000B     | Port C Pin status          |

| \$000C     | Port D Data Reg.           |

| \$000D     | Port D Data Direction Reg. |

| \$000E     | Port D Option Reg.         |

| \$000F     | Port D Pin status          |

|            |                            |

| \$0010     | ADC Control Reg.           |

| \$0011     | ADC Data Reg.              |

|            |                            |

| \$0012     | Watchdog Reg.              |

| \$0013     | LCD Ctrl. 1                |

| <b>***</b> |                            |

| \$0014     | EECR1                      |

| \$0015     | EECR2                      |

|            |                            |

| \$0016     | SIO Data Reg.              |

| \$0017     | SIO Interrupt Disable      |

| \$0018     | Timer Reg. 1               |

| \$0019     | Timer Reg. 2               |

| \$001A     | Timer Reg. 3               |

| \$001B     | Timer Reg. 4               |

| \$001C     | Timer Reg. 5               |

| \$001D)    | (Not to be used **         |

| )          | (                          |

| \$0023)    | (from \$001D to \$0023     |

| Family | Issuer Ref. | Chrono   | March 26, 1997                        | Previous Ref | Edition  |

|--------|-------------|----------|---------------------------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON                           |              | Target C |

| 517    | FG-KO       | 7282A5B5 | Kyz. Sus-inomson<br>Microellectronics | Page         | 7/23     |

# ST7282A5 - ST7282B5 - ROM FROM EPROM

| · · · · · · · · · · · · · · · · · · · |                            |

|---------------------------------------|----------------------------|

| \$0024                                | CRC Test Reg. ( ST use )   |

| \$0025                                | CRC Test Reg. (ST use)     |

| \$0026                                | Misc. Reg.                 |

| •                                     |                            |

| \$0027                                | LCD Ctrl. 2                |

|                                       |                            |

| \$0028                                | reserved                   |

| \$0029                                | reserved                   |

|                                       |                            |

| \$002A                                | Filter Reg. 1              |

| \$002B                                | Filter Reg. 2              |

|                                       |                            |

| \$002C                                | RDS_R0                     |

| \$002D                                | RDS_R1                     |

| \$002E                                | RDS_R2                     |

| \$002F                                | reserved                   |

|                                       |                            |

| \$0030                                | RDS_BD_H                   |

| \$0030<br>\$0031                      | RDS_BD_L                   |

| \$0032                                | RDS_CORRP                  |

| \$0032<br>\$0033                      | RDS_QU                     |

|                                       |                            |

| \$0034<br>\$0035                      | RDS_INT                    |

| \$0035<br>\$0036                      | reserved                   |

| \$0036<br>\$0037                      | reserved                   |

| \$0037                                | reserved                   |

|                                       |                            |

| \$0038                                | reserved                   |

| \$0039                                | reserved                   |

| \$003A                                | reserved                   |

| \$003B                                | reserved                   |

| \$003C                                | reserved                   |

| \$003D                                | reserved                   |

| \$003E                                | reserved                   |

| \$003F                                | reserved                   |

|                                       |                            |

| \$0040                                | LCD RAM 8 Byte MUX8        |

| φυυ <del>τ</del> υ<br>                | SEG7-0 = Byte 40 47        |

| \$0047                                | BP1 BP8 = Bit0 Bit7        |

| φ004 <i>1</i>                         |                            |

| \$0048                                | LCD RAM 24 Byte MUX8,11,16 |

| φυυ <del>τ</del> υ<br>                | SEG. 1 - 24 = Byte 48 5F   |

| \$005F                                | BP1 BP8 = Bit0 Bit7        |

| φυσσι                                 |                            |

| Family | Issuer Ref. | Chrono   | March 26, 1997   | Previous Ref | Edition  |

|--------|-------------|----------|------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON      |              | Target C |

| 517    | PG-RU       | 7282A5B5 | MICROELECTRONICS | Page         | 8/23     |

| \$0060                               | LCD RAM 4 Byte Mux 4               |

|--------------------------------------|------------------------------------|

|                                      | Seg -8, -9, -10, -11               |

| \$0063                               | BP1 BP4 = Bit0 Bit3                |

| \$0064<br>\$0065<br>\$0066<br>\$0067 | LCD RAM<br>not used<br>for display |

| \$0068                               | LCD RAM 24 Byte MUX 11, 16         |

|                                      | SEG. 1-24 = Byte 68 7F             |

| \$007F                               | BP9 BP16 = Bit0 Bit7               |

| \$0080<br><br>\$008F                 | reserved                           |

| \$0090                               | Port E Data Register               |

| \$0091                               | Port E Data Direction Register     |

| \$0092                               | Port E Option Register             |

| \$0093                               | Port E Pin Status                  |

| \$0094                               | Port F Data Register               |

| \$0095                               | Port F Data Direction Register     |

| \$0096                               | Port F Option Register             |

| \$0097                               | Port F Pin Status                  |

| \$0098                               | Port G Data Register               |

| \$0099                               | Port G Data Direction Register     |

| \$009A                               | Port G Option Register             |

| \$009B                               | Port G Pin Status                  |

| \$009C                               | Port H Data Register               |

| \$009D                               | Port H Data Direction Register     |

| \$009E                               | Port H Option Register             |

| \$009F                               | Port H Pin Status                  |

| \$00A0<br><br>\$03FF                 | RAM 864 Stack = 300-3FF            |

| Family | Issuer Ref. | Chrono                                      | March 26, 1997 | Previous Ref | Edition  |  |

|--------|-------------|---------------------------------------------|----------------|--------------|----------|--|

| ST7    |             | 97115                                       | SGS-THOMSON    |              | Target C |  |

| 517    | FG-KU       | PG-RO 7282A5B5 SLS-IHOMSON MICROELECTRONICS |                | Page 9/23    |          |  |

# ST7282A5 - ST7282B5 - ROM FROM EPROM

| \$0400<br><br>\$0DFF | reserved                   |

|----------------------|----------------------------|

| \$0E00<br><br>\$0E0F | EEPROM read out protected  |

| \$0E10<br><br>\$0FFF | EEPROM 512                 |

| \$1000<br><br>\$1FFF | not available (test area)  |

| \$2000<br><br>\$7FFF | reserved                   |

| \$8000<br><br>\$FFDF | ROM 32k                    |

| \$FFE0<br><br>\$FFEF | reserved (ST Routram area) |

| \$FFF0<br><br>\$FFFF | user vectors               |

"Not to be used" is mandatory. Any access would modify the functionality.

| Family | Issuer Ref. | Chrono   | March 26, 1997                        | Previous Ref | Edition  |

|--------|-------------|----------|---------------------------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON                           |              | Target C |

| 517    | PG-RU       | 7282A5B5 | Kyz. Sus-inomson<br>Microellectronics | Page         | 10/23    |

# **2 IMPLEMENTATION REMARKS OF THE DEDICATIONS**

In this chapter the options of the dedications, which are implemented are described. The dedications are described in detail in the target specs of the dedications. In case of discrepancies between this specification and the specs. of the dedications, this specification is valid.

#### 2.1 Core

#### 2.1.1 Oscillator

The oscillator can be used with quartz or ceramic resonator. The pins OSCIN and OSCOUT permit connection to the on chip clock oscillator circuit. OSCIN is the input, OSCOUT the clock oscillator output. A quartz or a ceramic resonator can be connected to these pins. Two external ceramic capacitors of 22pF connect the oscillator pins to ground. Also an external system clock can be applied to the oscillator input OSCIN.

#### 2.1.2 External reset input RESET

Low level active external reset input with Schmitt-Trigger characteristic. A pull-up resistor of typically  $300k\Omega$  ( $200k\Omega - 500k\Omega$ ) is integrated. This pin is resetting the I/O ports immediately without any need of a clock.

#### 2.1.3 Stack

The Stack is located at 3FFH and may go down to 300H.

#### 2.1.4 Interrupts

I1 is connected to IOPorts A ... H (start address FFFAH )

I2 is connected to RDS GRP & BLK SYNC (block interrupt) (start address FFF8H)

I3 is connected to SIO (start address FFF6H)

I4 is connected to Timer (start address FFF4H)

I5 is connected to ADC (start address FFF2H)

I6 is connected to RDS GRP & BLK SYNC (bit interrupt) (start address FFF0H )

If more then 1 input pin of a group, connected to the same interrupt, is selected as interrupt input with pullup, all selected inputs are "AND" connected.

#### WARNING :

Read modify write instructions may clear interrupt flags of dedications unintentionally if the interrupt flag is set after the read and before the write. Operations on control registers of dedications should be done with sufficient timing distance to interrupt events.

#### 2.1.5 Miscellaneous register( 0026h )

Read/Write

Reset Value: 0000 0000 ( 00h )

This register is a various 8-Bit register where only 3 bits are used for interrupt and slow mode.

- b6 = INTP: Interrupt Positive allows to select the I1 line triggering mode in conjunction with INTN. It can only be modified when the I bit of the CCR is set.

- b5 = INTN: Interrupt Negative allows to select the I1 line triggering mode in conjunction with INTP. It can only be modified when the I bit of the CCR is set.

- b1 = SM: Slow Mode. Setting this bit to "1" enables Slow Mode, thus reducing power consumption. In this mode, an extra divider by 64 is added in the clock circuitry. In Halt Mode SM bit is automatically reset.Registers of all RDS-Modules should not be accessed during slow mode.

| Family | Issuer Ref. | Chrono   | March 26, 1997   | Previous Ref | Edition  |

|--------|-------------|----------|------------------|--------------|----------|

| ST7    |             | 97115    | SGS-THOMSON      |              | Target C |

| 517    | PG-RO       | 7282A5B5 | Microelectronics | Page         | 11/23    |

| INTP | INTN | I1 External Interrupt Options         |

|------|------|---------------------------------------|

| 0    | 0    | Negative edge and Low level sensitive |

| 0    | 1    | Negative edge only                    |

| 1    | 0    | Positive edge only                    |

| 1    | 1    | Positive and negative edge sensitive  |

#### Figure 2. External Interrupt Options

#### 2.2 LCD controller/driver

The LCD module contains an LCD controller/driver with 20 segment and 16 backplane outputs able to drive up to  $20 \times 16 = 320$  segments. The LCD control logic reads automatically data from the LCD-RAM independently from the ST72 core.

Two signals (LCF32K,LCSYNCHINOUT) can be activated on pins PC0, PC1 to connect a slave display chip for expanding the number of segments. To activate these pins as LCF32K, LCSYNCHINOUT, bit0 of register LCD Ctrl.2 (0027H) has to be set. During reset this bit is cleared.

#### V<sub>LCD</sub> must never be below V<sub>DD</sub>.

#### 2.2.1 Address mapping of the picture elements

The LCD-RAM is located in the address region of the ST72 data space from address 40H - 7FH.

The LCD forms a matrix of 20 segment lines ( columns ) and 16 backplane lines ( rows ). Each bit of the LCD-RAM is mapped to one dot of the LCD matrix according to fig. 1. If a bit is set, the corresponding LCD segment is switched on, if it is reset, the segment is switched off.

After reset, the LCD-RAM is not initialized and contains arbitrary information. As the LCD control register is cleared, the LCD is completely switched off.

In halt mode no clock for the LCD module is available from the main oscillator. The LCD module is switched off in halt mode.

The input frequency of the LCD controller is f<sub>OSC</sub>/2 (4.275MHz).

A 32kHz stand by oscillator is not available. Therefore the mode FEXT ( $C_5$ ,  $C_4$ ,  $C_3 = 001$ ) of LCD control register cannot be used.

In any case a missing LCD clock ( no oscillator active, broken crystal etc. ) is detected by a clock supervisor circuit which switches all segment and common lines to ground to avoid destructive DC levels at the LCD.

If the LCD clock is not missing but far too slow (e.g. due to incorrect setting of  $C_5$ ,  $C_4$ ,  $C_3$  in LCD control register) the LCD is switched off periodically. This situation has to be avoided.

A division factor of +256 is recommended for the prescaler ( $C_5$ ,  $C_4$ ,  $C_3 = 110$ ;  $f_{OUT} = 16.699$ KHz). With this setting of the predevider, frame frequencies of 132.2Hz, 66.1Hz, 44.1Hz and 33.1Hz can be generated.

The frequency out of the prescaler must not be below 15KHz in order not to switch off the display through the LCD oscillator supervisor.

To activate segments and backplanes, data and option register bits of the corresponding combiport pins have to be set to 1. During reset data and option register bits of combiports are set to 1.

| Family      | Issuer Ref. | Chrono   | March 26, 1997   | Previous Ref | Edition  |

|-------------|-------------|----------|------------------|--------------|----------|

| <u>ет</u> 7 |             | 97115    | SGS-THOMSON      |              | Target C |

| ST7         | PG-RO       | 7282A5B5 | MICROELECTRONICS | Page         | 12/23    |

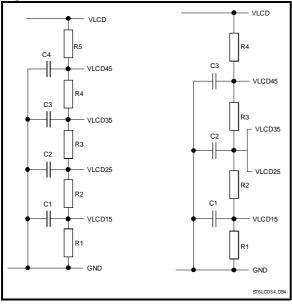

#### 2.2.2 External Divider Chain

The different display voltage levels are supplied by an external resistor chain as shown in fig. below. Two different configurations with five or four display voltage levels can be chosen.

The resistors have to have a good matching within < 1% to avoid DC voltage levels on the liquid crystal device.

DC levels trigger electrode reactions on the liquid crystal cell, deteriorating display quality rapidly.

#### Figure 3. External Divider Chain

$C_1 = C_2 = C_3 = C_4 = 0.1 \dots 0.3 \mu F$

| Family | Issuer Ref. | Chrono   | March 26, 1997   | Previous Ref | Edition  |

|--------|-------------|----------|------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON      |              | Target C |

| 317    | PG-RO       | 7282A5B5 | MICROELECTRONICS | Page         | 13/23    |

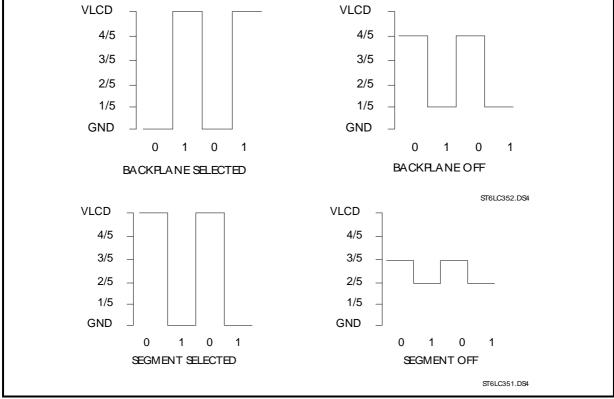

#### 2.2.2.1 Working with 1/5 Bias

| Family | Issuer Ref. | Chrono   | March 26, 1997   | Previous Ref | Edition  |

|--------|-------------|----------|------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON      |              | Target C |

| 517    | PG-RU       | 7282A5B5 | ATZ. SGS-IHOMSON | Page         | 14/23    |

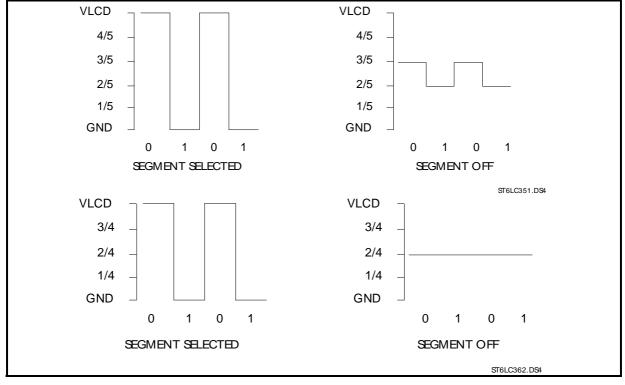

#### 2.2.2.2 Working with 1/4 Bias

Depending on the selected display material, the operating mode and the display voltage  $V_{LCD}$ , it is possible to reduce the LCD resistor chain to 4 resistors, and operate with the 1/4 bias method.

If VLCD35 and VLCD25 are connected to the same voltage, the segment and backplane drivers will work in the same way as with 1/5 bias, but the resulting waveforms will look a bit different :

Figure 5. Waveform on common and on segment output working with Bias 1/4

| Family | Issuer Ref. | Chrono   | March 26, 1997 | Previous Ref | Edition  |

|--------|-------------|----------|----------------|--------------|----------|

| ST7    | PG-RO       | 97115    |                |              | Target C |

| 317    | PG-RU       | 7282A5B5 |                | Page         | 15/23    |

| BP1<br>BP2<br>BP3<br>BP4<br>BP5<br>BP6<br>BP7<br>BP8 | bit0<br>bit1<br>bit2<br>bit3<br>bit4<br>bit5<br>bit6<br>bit7 | 48               | 49               | <br>4F           | 50               | <br>              | <br> | 5E | 5F                | ADRESSES<br>40 47<br>and 60 67<br>not used |

|------------------------------------------------------|--------------------------------------------------------------|------------------|------------------|------------------|------------------|-------------------|------|----|-------------------|--------------------------------------------|

| BP1<br>BP2<br>BP3<br>BP4<br>BP5<br>BP6<br>BP7<br>BP8 | bit0<br>bit1<br>bit2<br>bit3<br>bit4<br>bit5<br>bit6<br>bit7 | 68               | 69               | <br>6F           | 70               | <br>7B            | <br> | 7E | 7F                |                                            |

|                                                      |                                                              | S<br>E<br>G<br>1 | S<br>E<br>G<br>2 | S<br>E<br>G<br>8 | S<br>E<br>G<br>8 | S<br>E<br>G<br>20 |      |    | S<br>E<br>G<br>24 | (SEG21 SEG24<br>are not available)         |

#### Figure 6. Address Mapping of the LCD-RAM MUX16

## Figure 7. Address Mapping of the LCD-RAM MUX8

| BP1<br>BP2<br>BP3<br>BP4<br>BP5<br>BP6<br>BP7<br>BP8 | bit0<br>bit1<br>bit2<br>bit3<br>bit4<br>bit5<br>bit6<br>bit7 | 40                | 41                | <br>47           | 48               | 49               | <br> | <br> | 5E | 5F                | ADRESSES<br>60 7F<br>not used      |

|------------------------------------------------------|--------------------------------------------------------------|-------------------|-------------------|------------------|------------------|------------------|------|------|----|-------------------|------------------------------------|

|                                                      |                                                              | S<br>E<br>G<br>-7 | S<br>E<br>G<br>-6 | S<br>E<br>G<br>0 | S<br>E<br>G<br>1 | S<br>E<br>G<br>2 |      |      |    | S<br>E<br>G<br>24 | (SEG21 SEG24<br>are not available) |

| Family | Issuer Ref. | Chrono   | March 26, 1997         | Previous Ref | Edition  |

|--------|-------------|----------|------------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON            |              | Target C |

| 317    | FG-KO       | 7282A5B5 | Kyz. Sucroellectronics | Page         | 16/23    |

| BP1<br>BP2<br>BP3<br>BP4 | bit0<br>bit1<br>bit2<br>bit3 | 60                 | 61                 | 62                | 63                | 40                | 41                | <br>47           | 48               | 49               | <br> | <br>5E | 5<br>F            | ADRESS<br>ES<br>64 7F<br>not used        |

|--------------------------|------------------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|------------------|------|--------|-------------------|------------------------------------------|

|                          |                              | S<br>E<br>G<br>-11 | S<br>E<br>G<br>-10 | S<br>E<br>G<br>-9 | S<br>E<br>G<br>-8 | S<br>E<br>G<br>-7 | S<br>E<br>G<br>-6 | S<br>E<br>G<br>0 | S<br>E<br>G<br>1 | S<br>E<br>G<br>2 |      |        | S<br>E<br>G<br>24 | (SEG21<br>SEG24<br>are not<br>available) |

Figure 8. Address Mapping of the LCD-RAM MUX4

#### 2.3 TIMER 4

16 bit autoreload timer with 2 capture inputs connected to PA0, PA1 (see spec. ST7TIM4). The in-

#### 2.4 WATCHDOG

The WD2 is used to reset the ST7282 B5 after a certain period of time in the range of 2.8 msec up to 184 msec when  $f_{OSC} = 8.55$  MHz is used.

WD2 will be activated, if bit0 in Watchdog Reg. (Adr. 12h) is set ("1"). Once WD2 is running, any software access to bit0 in Watchdog Reg. will <u>NOT</u> influence WD2. However, a RESET signal (either externally or caused by WD2) will reset bit0 of Watchdog Reg.

#### **2.5 I/O PORTS**

Pins PD0 ... PD7, PE0 ... PE3, PF0 ... PF7, PG0 ... PG7 and PH0 ... PH7 are of type LCIO.

Pins PA0 ... PA7, PB0 ... PB7 and PC0 ... PC7 are of type IO3 and can also be used as analog inputs.

The interrupt outputs of PORT A, PORT B, PORT C, PORT D, PORT E, PORT F, PORT G and PORT H are anded and connected to the interrupt input 11 of core (start address FFFAH). So every port pin which is programmed as an input with interrupt enabled can generate an interrupt. If more than one port pin is programmed as an interrupt input, overlapping interrupts cannot be detected due to the AND function.

PA0, PA1 are also used as CP1, CP2 inputs of TIMER 4.

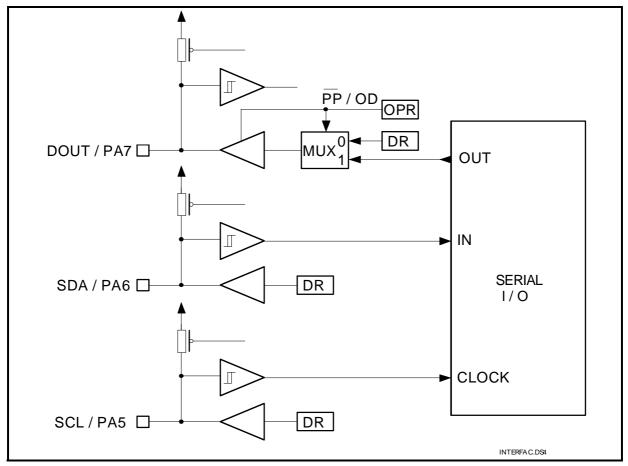

The pins PA5 ... PA7 are also used by the serial I/O (see fig. 2). PA5 is connected with SCL (

put clock of the timer is fosc divided by 2.

After a RESET, WD2 is deactivated and set to it's longest period (184 msec for  $f_{OSC} = 8.55$  MHz). WD2 is able to produce a SW-Reset (bit0 set to "1", bit1 to "0").

Dedication address of WD2 is 12h.

If WD2 is enabled, any stop instruction will generate a reset. However, the use of a stop instruction (HALT) is not recommended in this case.

clock input ), PA6 is connected with SDA ( data input ) and PA7 is connected with DOUT ( data output ) of the SIO.

For serial input operation PA5 and PA6 have to be programmed as inputs. For serial output PA7 has to be programmed as open drain output ( DDR = 1, OPR = 0 ). In this operation mode the output of the SIO shift register instead of the port data register is connected to the port buffer. When PA7 is programmed as push pull output ( DDR = 1, OPR = 1 ), the port data register is connected to the port buffer.

When the SIO pins are not used PA5 ... PA7 can be used as any other I/O pin (PA7 not in open drain output mode).

After reset ports PA0 ... PA7, PB0 ... PB7 and PC0 ... PC6 are in input mode with pull up resistors switched on and interrupt disabled.

| Family | Issuer Ref. | Chrono   | March 26, 1997   | Previous Ref | Edition  |

|--------|-------------|----------|------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON      |              | Target C |

| 517    | FG-RO       | 7282A5B5 | MICROELECTRONICS | Page         | 17/23    |

PA4 does not have a pull-up resistor.

Ports PD0 ... PD7, PE0 ... PE3, PF0 ... PF7, PG0 ... PG7 and PH0 ... PH7 are in the "LCD Output mode" (all pins switched to  $V_{SS}$ ).

#### 2.6 ADC

The reference voltage inputs of the ADC1N are connected to  $V_{DDA}$ ,  $V_{SSA}$ . Therefore special care has to be taken to stabilize  $V_{DDA}$ ,  $V_{SSA}$  and to avoid switching of I/O pins during conversion. Analog inputs may be multiplexed from pins PA0 ... PA7, PB0 ... PB7 and PC0 ... PC7. Up to 24 analog inputs can be multiplexed.

Selection of an analog input is done by programming the corresponding pin of a port as analog input (DDR = 0, DR = 1, OPR = 1). Be sure that only one port pin is programmed as analog input at a time. Otherwise the analog sources are shorted by the analog multiplexer. Conversion time for an 8.55 MHz clock is 34  $\mu$ sec (i.e. 288 clocks + 0...6 clocks of f<sub>OSC</sub>) because the ADC is supplied with a clock signal of f<sub>OSC</sub> : 6 that is also available dur-

#### 2.7 SERIAL I/O

The 8 bit SIO generates an interrupt after the falling edge of the eight external clock pulse. The interrupt signals to the ST72 to read or write the SIO via an 8 bit register (adr. 26H).

The SIO uses the input/output structure of Port A ( PA5 : SCL, PA6 : SDA, PA7 : DOUT ) (see fig. 2).

The 3 pins can be operated in the following ways: directly by software, as an S-BUS, as an  $I^2$ C-BUS and as a standard SIO ( clock, data, enable ).

<u>PC7 is switched to analog input mode during reset</u> (data register and option register bits are set).

PC0, PC1 may optionally be used to "cascade" the LCD (refer to: 2. LCD CONTROLLER/DRIVER).

ing WAIT. The ADC interrupt is connected to level sensitive interrupt input I5 of the core (start address FFF2H). So the interrupt has to be cleared before the interrupt service routine is left.

A stop instruction will stop the clock of the ADC and will switch off its comparator to achieve minimum power consumption. This can also be done by clearing bit 5 (SC) of ADC control register (10H).

A rising edge on EOC-bit sets the interrupt flipflop. To remove the interrupt, a write operation to ADC-Control register has to be executed, to clear the interrupt flipflop. After the reset, the interrupt flipflop is also cleared.

To operate the SIO PA5 and PA6 have to be programmed as inputs, PA7 as open drain output. The SIO interrupt (active low) is connected to the interrupt input I3 of the core (address FFF6H).

After reset all ports are in input mode with pull up resistors switched on and the SIO interrupt is disabled.

| Family | Issuer Ref. | Chrono   | March 26, 1997                       | Previous Ref | Edition  |

|--------|-------------|----------|--------------------------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON                          |              | Target C |

| 517    | FG-RO       | 7282A5B5 | Kyz, Sus-inomson<br>Microelectronics | Page         | 18/23    |

Figure 9. Peripheral Interface Configuration of Serial I/O

#### 2.8 RAM

The RAM is located in the address range A0H-3FFH.

300H-3FFH may be used as Stack area.

#### 2.9 EEPROM

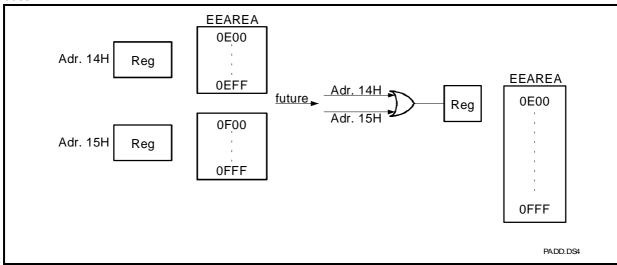

The 512 bytes EEPROM is located at addresses 0E00 - 0FFF. 2 cells of 256 bytes each or one cell of 512 bytes may be used. EEPROM control register EECR (adr. 014H) is used to control the different operation modes of the range 0E00H - 0EFFH, EEPROM control register EECR2 (adr. 015H) that of range 0F00H - 0FFFH. Some of its bits are read only, some are write only. <u>So no single bit instructions are allowed</u>.

To avoid destruction of data during power up or down, the reset pin directly desactivates the chargepump of EEPROM cells.

The EEPROM can be used for data storage only, no program execution and no read modify write in-

structions (single bit, increment, decrement) are possible.

After bit E2LAT of EECR goes to low, there should not be a read operation during the next 20  $\mu sec.$

A parallel programming mode for 8 bytes is available. No clear is needed before a write.

Two cells of 256 bytes are used, parallel programming of bytes in each cell is possible. This should be avoided however, to keep software compatitility between all future versions and ROM versions, that have only one physical register, that will be addressed through two different addresses 14H and 15H.

| Family | Issuer Ref. | Chrono   | March 26, 1997   | Previous Ref | Edition  |

|--------|-------------|----------|------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON      |              | Target C |

| 317    | FG-KO       | 7282A5B5 | MICROELECTRONICS | Page         | 19/23    |

Before access to one area, also the control register of the other area should be checked and access done only, if both areas allow the required access. SGS-THOMSON may implement a single or double register version in future ROM or EPROM versions.

#### 2.10 32K ROM

The 32K ROM is located at addresses 8000H-FFFFH. 16 bytes (FFE0H - FFEFH) are reserved for SGS-Thomson test vectors.

#### 2.11 RDS

Modules (see separate specs)

Registers of all RDS-Modules should not be accessed (read or write) during slow mode of CPU.

#### 2.12 OSCILLATOR

The ST7 Oscillator allows operation with a crystal or external input. The corresponding mode is defined by a metal option. In case of external input the clock amplitude into OSCI may not be lower then 50mV. The pin OSCO/STOP then is serving as output for the stop signal to synchronize with external clock sources.

In the present version, the device works with a dedicated crystal.

| Family | Issuer Ref. | Chrono   | March 26, 1997        | Previous Ref | Edition  |

|--------|-------------|----------|-----------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON           |              | Target C |

| 317    | PG-KO       | 7282A5B5 | ATZ. MICROELECTRONICS | Page         | 20/23    |

# **3 TESTING**

Pin VPP/TEST is used for testing the device. For normal operation pin VPP/TEST has to be connected to  $V_{SS}$  or has to be left open. An internal pull down resistor of about 100k is integrated to

select normal operation mode if pin VPP/TEST is not connected.

The testmodes are for SGS THOMSON internal use only!

# **4 PIN DESCRIPTION**

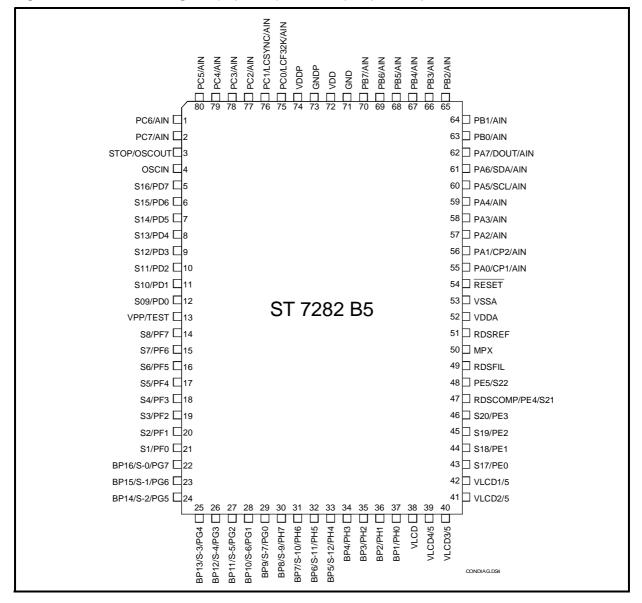

#### 4.1 Connection diagram

Figure 10. Connection Diagram (top view) for the 80 pin quad flat pack

| I | Family | Issuer Ref. | Chrono   | March 26, 1997             | Previous Ref | Edition  |

|---|--------|-------------|----------|----------------------------|--------------|----------|

| Ī | ST7    | PG-RO       | 97115    | SGS-THOMSON                |              | Target C |

|   | 317    | PG-RO       | 7282A5B5 | ATZ. SUS-INICROELECTRONICS | Page         | 21/23    |

# 4.2 PIN DESCRIPTION

| Ports A, B, C, D, E, F, G are described              | Ports A, B, C, D, E, F, G are described on page 18 |  |  |  |  |  |  |  |

|------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|

| STOP/OSCOUT<br>STOP/OSCIN                            | Oscillator pins                                    |  |  |  |  |  |  |  |

| VPP/TEST                                             | Test pin                                           |  |  |  |  |  |  |  |

| VLCD<br>VLCD 4/5<br>VLCD 3/5<br>VLCD 2/5<br>VLCD 1/5 | Voltage levels for the LCD module                  |  |  |  |  |  |  |  |

| NC                                                   | (not connected) - must be left open                |  |  |  |  |  |  |  |

| RDSCOMP<br>RDSFIL<br>MPX<br>RDSREF                   | I/O Pins for the RDS module (see seperate spec)    |  |  |  |  |  |  |  |

| VSSA<br>VDDA                                         | Analog voltages for the ADC and filter module      |  |  |  |  |  |  |  |

| VDD<br>GND                                           | Supply voltage                                     |  |  |  |  |  |  |  |

| VDDP<br>GNDP                                         | Peripheral supply voltage                          |  |  |  |  |  |  |  |

| Reset                                                | Reset pin - active low                             |  |  |  |  |  |  |  |

| Family | Issuer Ref. | Chrono   | March 26, 1997        | Previous Ref | Edition  |

|--------|-------------|----------|-----------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON           |              | Target C |

| 317    | PG-RO       | 7282A5B5 | ATZ. MICROELECTRONICS | Page         | 22/23    |

# **5 RELATED DOCUMENTS**

ST7 ADC2- SD 70K L138 ed. A ST7 RDS BD - SD 70K L145 ed. B ST7 RDS GB - SD 70K L144 ed. B ST7 RDS FI - SD 70K L129 ed. C ST7 SIO - # 96098 ed. B ST7 OSCILLATOR - SD 70K L163 ed. A ST7 LCIO1 - SD 70K L135 ed. C

ST7 IO3 - SD 70K L136 ed. B ST7 LCD4 - SD 70K L140 ed. B ST7 TIM4 - SD 70K L130 ed. A ST7 WD2 - SD 70K L137 ed. A ST7 EEPROMeep2a

# **6 HISTORIC**

Below, the differences between the original specification # 96096 ed. B (ST7282B5) and the present specification # 97115 ed. B:

| Page # modified in<br>original spec 96096 | Modifications                                                                                                                                               | New page       |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1                                         | Block diagram : S21, S22                                                                                                                                    | 2              |

| 2                                         | Quick reference : 2 commercial products                                                                                                                     | 3              |

| 3                                         | VLCD changed from target of 10V to < 7V<br>LU on all pins changed from target of class A to class A on all pins except<br>pin V <sub>DDA</sub> (52) class C | 3              |

| 4                                         | Islow changed from target of 1mA to 2mA;<br>Ihalt changed from target of 10μA to 100μA ;<br>VLCD changed from target of 10V to 7V.                          | 4 - 5          |

| 7                                         | Address mapping : TIMER                                                                                                                                     | 7 - 8 - 9 - 10 |

| 21                                        | EEPROM : 2 bank 256 bytes                                                                                                                                   | 19             |

|                                           | Oscillator                                                                                                                                                  | 20             |

| 23                                        | Connection diagram : S21, S22                                                                                                                               | 21             |

|                                           | Related documents, sales types                                                                                                                              | 23             |

# **7 ORDERING INFORMATION**

| SALES TYPE      | OPTIONS  | TEMP RANGE    | PACKAGE |  |

|-----------------|----------|---------------|---------|--|

| ST7282A5Q6B/XXX | NO LCD   | -40°C to 85°C | PQFP80  |  |

| ST7282B5Q6B/XXX | WITH LCD |               |         |  |

The user code to be delivered to SGS-THOMSON must be in Motorola S.format (.S19) and must

NOT include EEPROM content.

| Family | Issuer Ref. | Chrono   | March 26, 1997                  | Previous Ref | Edition  |

|--------|-------------|----------|---------------------------------|--------------|----------|

| ST7    | PG-RO       | 97115    | SGS-THOMSON<br>MICROELECTRONICS |              | Target C |

|        |             | 7282A5B5 |                                 | Page 23/23   |          |